Cov txheej txheem:

- Kauj Ruam 1: Tsim Cov Hluav Taws Xob Hluav Taws Xob

- Kauj Ruam 2: Teeb Tus Pin Planner

- Kauj ruam 3: Verilog Code

- Kauj ruam 4: Upload Verilog Code

Video: FPGA Cyclone IV DueProLogic Tswj Servo Tsav: 4 Kauj Ruam

2024 Tus sau: John Day | [email protected]. Kawg hloov kho: 2024-01-30 09:25

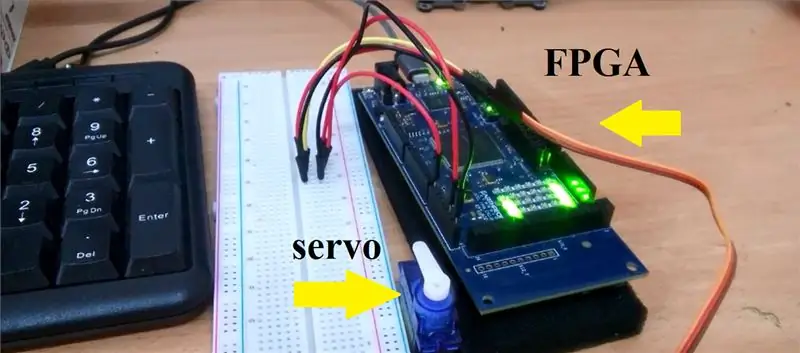

Hauv qhov kev qhia no, peb yuav sau Verilog code los tswj lub cav servo. Lub servo SG-90 yog tsim los ntawm Waveshare. Thaum koj yuav lub servo motor, koj tuaj yeem tau txais cov ntawv teev npe uas ua haujlwm qhov hluav taws xob, qhov siab tshaj plaws thiab qhov kev thov Pulse Width Modulation (PWM) … thiab lwm yam. Txawm li cas los xij, FPGA DuePrologic muab cov khoom siv hluav taws xob ntawm 3.3V qhov twg ua haujlwm qhov hluav taws xob ntawm servo SG -90 yog 5V - 7V. Hauv qhov tsis muaj hluav taws xob hluav taws xob, Kuv yuav sau kuv qhov ntsuas PWM txhawm rau txhawm rau tig lub cav servo kom ua tiav.

Peb txoj haujlwm: Lub cav servo tau tig rov qab los nrog lub sijhawm 5 vib nas this

Daim ntawv qhia tag nrho:

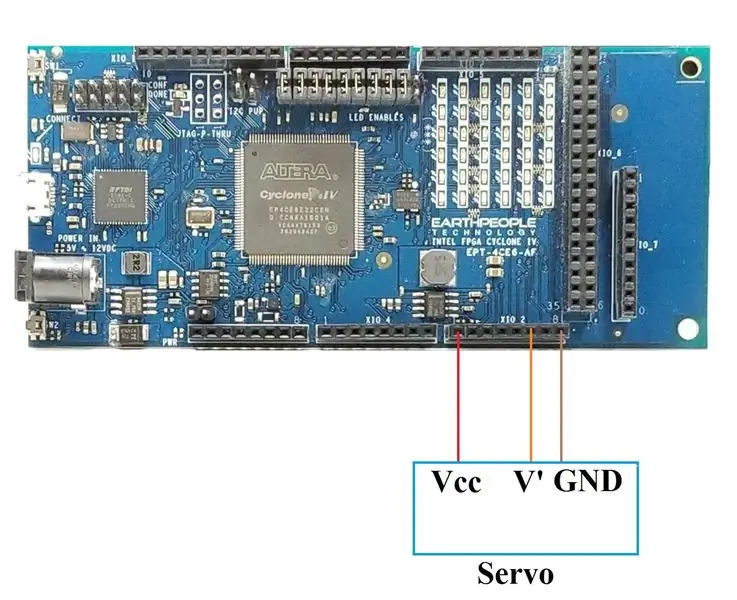

Kauj Ruam 1: Tsim Cov Hluav Taws Xob Hluav Taws Xob

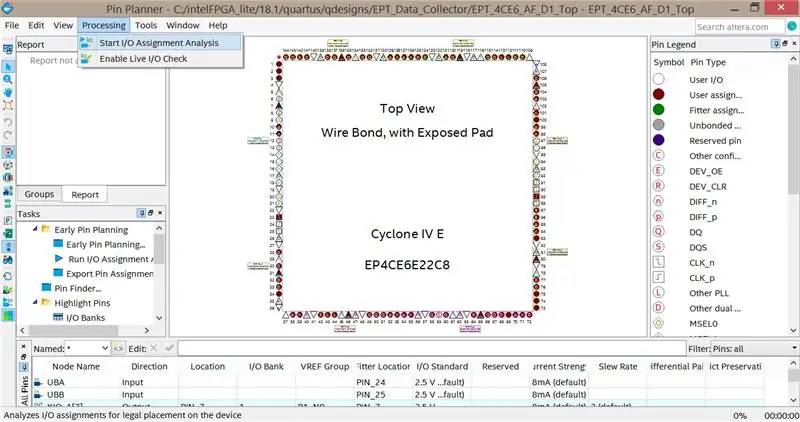

Kauj Ruam 2: Teeb Tus Pin Planner

Nyem "Pib I/O Assignment Analysis" txhawm rau txheeb xyuas yog tias tus pin phiaj xwm tau teeb tsa raug. Txwv tsis pub, koj yuav tsum ntshuam txhua lub npe chaw nres nkoj los ntawm koj tus kheej.

Kauj ruam 3: Verilog Code

Peb tsim lub sijhawm "servo_count". Thaum "servo_A" HIGH, PWM yog 1.5ms thiab yog li qhov servo nyob ntawm 120 deg. Hauv qhov sib piv, thaum "servo_A" LOW, PWM yog 0.15ms thiab yog li qhov kev pabcuam tseem nyob ntawm 0 degree.

muab XIO_2 [3] = servo_pulse; // rau V

reg [31: 0] servo_count;

pib pib

servo_count <= 32'b0;

servo_A <= 1'b0;

kawg

ib txwm @(posedge CLK_66)

pib

servo_count <= servo_count + 1'b1;

yog (servo_count> 400000000) // Clock cycle 66MHz, 1/66M * 400000000 ~ 5 vib nas this

pib

servo_A <=! servo_A;

servo_count <= 32'b0;

kawg

kawg

reg [31: 0] ex_auto;

pib pib

ex_auto <= 32'b0;

servo_auto <= 1'b0;

kawg

ib txwm @(posedge CLK_66)

pib

yog (servo_A == 1'b1)

pib

ex_auto <= ex_auto + 1'b1;

if (ex_auto> 100000) // Clock cycle 66MHz, PWM no yog ~ 1.5ms, servo tig mus rau 120 deg

pib

servo_auto <=! servo_auto;

ex_auto <= 32'b0;

kawg

kawg

yog (servo_A == 1'b0)

pib

ex_auto <= ex_auto + 1'b1;

if (ex_auto> 10000) // Clock cycle 66MHz, PWM no yog ~ 0.15ms, servo tig mus rau 0 deg

pib

servo_auto <=! servo_auto;

ex_auto <= 32'b0;

kawg

kawg

kawg

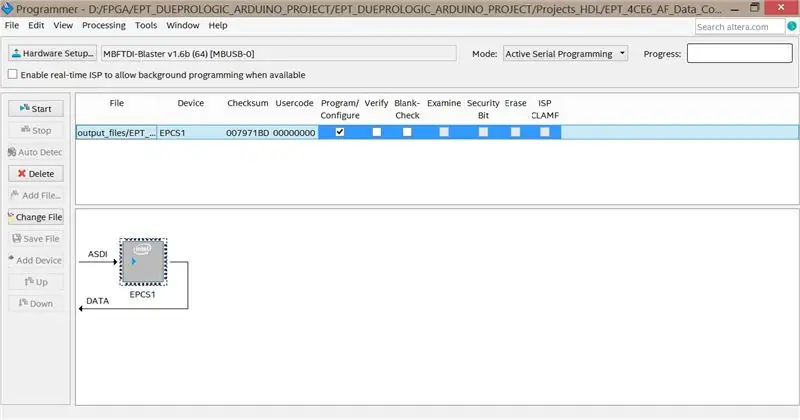

Kauj ruam 4: Upload Verilog Code

Nyem "Start Compilation". Yog tias tsis muaj lus yuam kev tshwm sim, mus rau "Programmer" kom ua tiav kev teeb tsa kho vajtse. Nco ntsoov hloov kho cov ntaub ntawv pof hauv "Hloov cov ntaub ntawv" yog tias tsim nyog. Nyem "Pib" txhawm rau upload cov cai.

Tom qab tag nrho, koj yuav tsum pom tias lub cav servo tau hloov pauv ib ntus.

Pom zoo:

FPGA Cyclone IV DueProLogic Tswj Raspberry Pi Lub Koob Yees Duab: 5 Kauj Ruam

FPGA Cyclone IV DueProLogic Tswj Raspberry Pi Lub Koob Yees Duab: Txawm hais tias FPGA DueProLogic raug tsim los rau Arduino, peb tab tom ua FPGA thiab Raspberry Pi 4B sib txuas tau. FPGA txhawm rau tig lub kaum sab xis ntawm

FPGA Cyclone IV DueProLogic - Laub Khawm & LED: 5 Kauj Ruam

FPGA Cyclone IV DueProLogic - Push Button & LED: Hauv qhov kev qhia no, peb yuav siv FPGA los tswj cov LED sab nrauv. Peb tab tom yuav ua tiav cov haujlwm hauv qab no (A) Siv lub pob nyem ntawm FPGA Cyclone IV DuePrologic los tswj LED. (B) Flash LED ntawm & tawm tsis tu ncua Daim vis dis aus lab

Yuav Ua Li Cas Siv Drone Quadcopter Brushless DC Tsav los ntawm Kev Siv HW30A Brushless Tsav Ceev Tswj thiab Servo Tester: 3 Kauj Ruam

Yuav Ua Li Cas Siv Drone Quadcopter Brushless DC Motor los ntawm Kev Siv HW30A Brushless Motor Speed Controller thiab Servo Tester: Nqe lus piav qhia: Cov cuab yeej no hu ua Servo Motor Tester uas tuaj yeem siv los ua haujlwm servo lub cev los ntawm kev ntsaws yooj yim hauv servo lub cev muaj zog thiab muab lub zog rau nws. Cov cuab yeej kuj tseem tuaj yeem siv ua lub cim hluav taws xob rau kev tswj hluav taws xob ceev (ESC), tom qab ntawd koj tuaj yeem

Fpga Tswj RC Servo Tsav Neeg Hlau Caj Npab - Kev Sib Tw Digilent: 3 Kauj Ruam

Fpga Controlled RC Servo Motor Robot Arm - Digest Contest: FPGA tswj servo lub cev muaj zog neeg hlau Cov txheej txheem yog ua raws Digilent Basys3 pawg thawj coj txhim kho thiab nws yuav muaj peev xwm ntawm cov khoom siv sib txuas

Pike - Tsav Kev Nyab Xeeb, Tsav Ntse, Tsav Tus Pike!: 5 Kauj Ruam

Pike - Tsav Kev Nyab Xeeb, Tsav Zoo, Tsav Pike!: Zoo siab txais tos rau kuv qhov project hu ua Pike! Nov yog qhov haujlwm raws li ib feem ntawm kuv txoj kev kawm. Kuv yog tub ntxhais kawm NMCT ntawm Howest hauv Belgium. Lub hom phiaj yog ua kom qee yam ntse los ntawm kev siv Raspberry Pi. Peb muaj kev ywj pheej tiav uas peb xav ua ntse.Rau rau kuv nws wa