Cov txheej txheem:

- Kauj Ruam 1: Quelques Hom De Mémoires

- Kauj Ruam 2: Mémoire Serial FRAM SPI

- Kauj Ruam 3: Cycles Serial FRAM

- Kauj Ruam 4: Code Pilotant La Mémoire FRAM

- Kauj Ruam 5: Mémoire Parralèle

- Kauj Ruam 6: Cycles Mémoire Parralèle

- Kauj Ruam 7: Code Pilotant La Memoire Parraléle

- Kauj Ruam 8: Txhawb Nqa Mémoires

Video: Extension Mémoire Pour BeagleBone Black: 8 Kauj Ruam

2024 Tus sau: John Day | [email protected]. Kawg hloov kho: 2024-01-30 09:27

Je vous présenter dans cet instructable un de mes projet qui consistait à piloter des mémoires de différents hom afin de pouvoir tester leur fonctionnement dans des conditions spatiales (enceinte radiative) et de trouver le taux d'erreurs engendré par cet enquire de chaque. Vous pouvez aussi utiliser les données de ce projet pour étendre la mémoire de votre BeagleBone, créer une clé USB ou simplement pour étudier leur fonctionnement.

Kauj Ruam 1: Quelques Hom De Mémoires

Voici une liste exhaustive des différents types de mémoires utilisés dans ce projet avec leurs avantages et une inconvénients:

Premier hom de mémoire: la mémoire SRAM

La mémoire vive statique (ou Static Random Access Memory) tsis yog hom de mémoire vive utilisant des bascules pour mémoriser les données. Contrairement à la mémoire dynamique, son content n'a pas besoin d'être rafraîchit périodiquement. Elle reste cependant volatile: elle ne peut se passer d'alimentation sous peine de voir ses xov xwm effacées tsis tuaj yeem hloov kho tau!

Avantages: - la SRAM est rapide (temps d'accès 6 à 25 ns) - peu coûteuse (4 €/Mo). Inconvénients: - besoin d'être alimenté en durability pour ne pas perdre ses données, aussi ce type de mémoire impose d'ajouter à notre carte mémoire un moyen de l'alimenter en kev nyob ruaj khov. Le moyen trouvé est d’ajouter un super condensateur Cellergy pouvant alimenter la mémoire pendant une journée.

Deuxième hom de mémoire: la mémoire MRAM

La mémoire vive statique magnétique (Magnetic Random Access Memory) stocke les données sans avoir besoin d’être alimentée. Le changement d'état se fait en changeant l'orientation polaire des électrons (par effet tunnel notamment). Elle yog qhov tseem ceeb tshaj plaws aux hluav taws xob thiab aux haute températures. Avantages:- la non-volatilité des informations. - inusabilité, puis ce qu'aucun mouvement électrique n'est engagé (endurance de 10^16 cycles lecture /écriture!). - la consommation électrique est théoriquement moindre puisqu'il n'y a pas de perte thermique due à la résistance des matériaux aux mouvements des électrons. - Lub sijhawm ntsuas ntawm 10 nanosecondes. - les débits sont de l'ordre du gigabit par thib ob. - tsis zoo heev résistance aux radiations, omniprésentes dans un milieu spatialInconvénients: - coûteuse (~ 35 €/Mo) tsheb encore en phase de développement (commercialization de masse du produit prévue en 2018!) mais on peut s'en procurer chez Digikey commercialisé sous la marque Everspin.- capacité de stockage est très limitée due aux champs magnétiques qui risquent de perturber les cellules voisines si elles sont trop proches les unes des autres.

Troisième hom de mémoire: la mémoire FRAM

La mémoireFRAM (Ferroelectric Random Access Memory) yog ib hom de mémoire d'ordinateur tsis hloov pauv hloov pauv hloov pauv à l'état de recherche et développement.

Elle yog similaire à la mémoire DRAM à laquelle ntawm ajouté une couche ferro-électrique pour obtenir la non volatilité. Nyob rau xyoo 2011, Texas Instruments lance le premier microcontrôleur à mémoire FRAM.

Leur kev siv yog destinée au SSD (Solid State Drive), comme pour les autres mémoires non volatiles, les données n'ont pas besoin d'énergie pour être conservées. Avantages: - une plus plus faible consommation d'Electricité. - une plus grande rapidité de lecture et d'écriture (temps d'accès de 100 nanosecondes contre 1 microseconde pour la mémoire flash). - la possibilité d'être effacée et réécrite un bien plus grand nombre de fois (endurance de 10^14 cycles lectures/écritures). Inconvénients: - des capacités de stockage plus limitées - un coût de fabrication plus élevé, ~ 30 €/Mo

Les deux grandes familles de mémoires: Série (duab 1) et parallèle (duab 2)

Série: les mémoires séries ont pour avantage de permettre un nce de qhov chaw thiab de garder la même teeb tsa selon les modèles d'où leur txhawb nqa kev koom tes. Cependant ces mémoires ne sont pas très rapide tsheb la trame entière (hom d'épération, adresse, données…) doit çtre reçue avant d’enregistrer ou accéder à la donnée. Kev ntaus cim la vitesse d'accès allant de 5 à 20MHz ntawm m au mieux accès aux bits de données que tous les (1/(20*10⁶)) sec soit 50 ns par bits (50ns*8 = 400ns ncuav 8 khoom). Ce hom de mémoire yog tsis siv cov lorsque le temps d’accès aux données à peu d'importance comme lors du chargement d'un BIOS dans certaines cartes de type FPGA.

Parallèle: Les mémoires parallèles sont très utilisées dans tous les domaines allant de la RAM pour ordinateur à la clé USB. Ce hom de mémoire yog beaucoup ntxiv rau rapide que la mémoire SPI tsheb en un coup d'horloge il permet d'accéder aux cov ntaub ntawv, nous sommes donc peev xwm de récupérer en quelques ms tout le content de la mémoire de 1Mo. L'inconvénient yog qhov nyuaj à intégrer tsheb les nombreux pins diffèrent d'un modèle à l'autre et la taille du boîtier est plus grande.

Pour accéder à plusieurs en mémoire en même temps nous devons jouer sur les pins de chip enable (CE) des mémoires afin d'indiquer à laquelle nous voulons accéder (voir schéma). Le schéma yog tus tsim nyog rau les deux hom de mémoires seul hloov pauv le moyen d'accès aux données et adresses.

Kauj Ruam 2: Mémoire Serial FRAM SPI

Câblage de la BeagleBone m la mémoire: Reliés au 3.3V: VDD, HOLD, WP A la masse: VSS MISO relié à SO MOSI relié à SI CS relié à CS

NB: L'avantage de ce hom de mémoire SPI est que, peu importe le modèle ou la marque du fabricant de semi-conducteurs, la configuration du boîtier reste la même ce qui n'est pas le cas des autres hom de mémoires comme les mémoires sib piv De plus les sheet de de différentes mémoires indiquent que toutes fonctionnent de la même manière. Ainsi il yog qhov ua tau los ntawm cov neeg caij npav sib txawv ntawm cov qauv sans avoir à programmer de nouveaux algorithmes.

Les pins HOLD et WP sont reliés au 3.3V: si cela empêche l'utilisateur d'utiliser ces fonctionnalités, cela permet de faciliter la programmation. Kev ywj pheej ces fonctionnalités auraient été utiles si l'on avait plusieurs mémoires SPI à tus tsav dav hlau!

Afin de piloter la mémoire il faut d'abord étudier sa fiche cov txheej txheem tsis muaj peev xwm à l'adresse suivante:

Cette fiche cov txheej txheem sib txawv sib txawv mus rau nécessaires pour lire et écrire dans la mémoire et ainsi réaliser un program permettant de les piloter.

Kauj Ruam 3: Cycles Serial FRAM

Ecriture:

Avant d'écrire dans la mémoire il faut envoyer une trame d'accès à L'écriture (WREN) 0000 0110 (0x06h) (Saib daim duab 5) Txheeb xyuas de la trame d'écriture envoyée par MOSI de la Beaglebone à SI (Saib daim duab 9)

- 8 qhov tseem ceeb ua ntej, Op -code de l'écriture (NYEEM): 0000 0011 (0x03h) - 16 khoom ntxiv, m sime si cette mémoire n'en considère que 11 tsheb il s'agit d'une mémoire de 16Kb ((2 ^11)*8bits) il faut envoyer 16 bits car cela permettra de pouvoir aussi piloter des mémoires 64Kb. - 8 khoom ntawm données. Kev qhuab qhia:

Txheeb xyuas de la trame de qhuab qhia tus neeg sawv cev MOSI de la Beaglebone à SI: (Saib daim duab 10)- 8 qhov tseem ceeb ua ntej, Op-code de la qhuab qhia (WRITE): 0000 0010 (0x02h)- 16 cov khoom ntxiv Txheeb xyuas de la trame de qhuab qhia envoyée par SO à MISO de la Beaglebone: - 8 khoom de données

Kauj Ruam 4: Code Pilotant La Mémoire FRAM

Pour compiler ce program en langage C: $ gcc programme_spi.c spo spiPour utiliser ce program: $./spi add1 ntxiv 2 hom ntaub ntawv

Ntxiv 1 (MSB) thiab Ntxiv 2 (LSB) tus neeg sib tham chacun à 8 khoom de donnée, cov ntaub ntawv sib xws à 8 khoom de données à écrire (mettre 0 si qhuab qhia) Hom sib tham à l'écriture (= 2) ou la qhuab qhia (= 1).

Piv txwv ntawm kev siv:./spi 150 14 210 2 écrit à l'adresse 16 khoom 150 14 (0x96h, 0x0Eh) la donnée 210 (0xD2).

./spi 150 14 0 1 lit à adresse150 14 (0x96h, 0x0Eh)

Kauj Ruam 5: Mémoire Parralèle

Pour ce projet j'ai utilisé la mémoire SRAM ALLIANCE AS6C1008 128Kb * 8 khoom (voir schéma)

Configuration du boitier: 17 Adresses: A0-A16 8 Data: D0-D7 2 Chip Enable: CE#-CE2 2 Write et Output Enable: WE#-OE#2 VCC (3.3V), VSS (GND) 1 tsis txuas: NCO

NB: La disposition des pins varie grandement d'un modèle à un autre ainsi que les temps de lecture / écriture

Pour le câblage à la BeagleBone voir schéma (Un réel plaisir à débugger où lorsque l'on à mal câblé!)

Ceevfaj: Vous vous demandez sans doute pourquoi j'ai sauté lees paub GPIO dans les lignes d'adresses thiab cov ntaub ntawv, c'est tout simplement que ces GPIO sont alloués à l'EMMC présent sur la BBB et que malgré mes recherches je n'ai jamais réussi à utiliser correctement (me faisant perdre au passage 2 semaines tsheb je pensais la mémoire défectueuse alors que certains GPIO ne fonctionnaient simplement pas!)

Afin de piloter la mémoire il faut d'abord étudier sa fiche cov txheej txheem tsis muaj peev xwm ad l'adressesuivante:

Cette fiche cov txheej txheem tsis sib xws hauv kev ua haujlwm nécessaires pour lire et écrire dans la mémoire et ainsi réaliser notre program. Afin d'écrire dans la mémoire il faut respecter le cycle imposé par les constructeurs, qui sont tous les mêmes pour chacune des mémoires utilisées. Ainsi n'importe quelle mémoire 64Kb peut fonctionner avec notre program (si correctement câblé:)) Kev ywj pheej les temps entre les cycles peuvent varier d'une mémoire à une autre, le cycle le plus long (100ns) des mémoires utilisées étant retenu tsheb il s'adaptera à toutes les mémoires. Ainsi les temps déériture et qhuab qhia yam tsawg kawg ib xyoos ib zaug par les constructeurs ne seront jamais koom nrog kev tsheb tsis zoo par la mémoire la plus lente. La durée des cycles yog définie dans le code. Le seul moyen d’aller d’atteindre la vitesse maximale et de programmer les cycles pour une mémoire en particulier avec les temps minimaux. Le cycle déériture revive à modifier l'état des GPIOs. La base du code est celle qui permet de faire clignoter une LED en ajoutant des temporisations précises correspondant aux durées des cycles imposées par le constructeur. En effet l'action de faire clignoter une LED sib tham à la création de cycles d'état haut et bas pour les GPIOs.

Le cycle de qhuab qhia quant à lui suav nrog en la récupération de l'état des GPIO, comme pour détecter l'état d'un bouton poussoir.

Kauj Ruam 6: Cycles Mémoire Parralèle

Cycle d'écriture (daim duab 1, 2):

Pour écrire dans la mémoire il suffit de mettre les pins d'adresse aux valeurs souhaitées puis d'activer les entrées chip enable CE à l'état haut et l'instruction Sau ntawv pab kom WE. Une fois cela effectuer mettre les pins des données aux valeurs souhaitées et le ncig saib yog joué (Mais mloog tout de même à bien respecter les temporisations! ~ 100ns)

Cycle de lecture (daim duab 3, 4):

Pour écrire dans la mémoire il suffit de mettre les pins d'adresse aux valeurs souhaitées puis d'activer les entrées chip enable CE à l'état haut et l'instruction Output enable OE. Une fois cela effectué on récupère sur les entrée GPIO de la BeagleBone les valeurs se trouvant à cette adresse.

Kauj Ruam 7: Code Pilotant La Memoire Parraléle

Ce code permet de piloter 2 mémoire parallèles indépendamment l'une de l'autre et s'utilise comme ceci:

muab tso ua ke: $ gcc -lm programme_memoire.c -o memoire

$./memoire ntxiv 1 ntxiv 2 data1 data2 hom slot1 slot2

hom: 1 Lecture, 2 Ecriture

Le code étant créer pour piloter deux mémoires il y a deux "slots", mettre à 1 pour utiliser.

Ex: $./memoire 120 140 20 210 2 1 0

écrit à l'adresse 120 140 (hex 16 khoom) les données 20 210 sur la mémoire sur le slot 1.

Ex: $./memoire 120 140 0 0 1 11 1

lit à adresse 120 140 les données sur la mémoire du slot 1 et 2.

Kauj Ruam 8: Txhawb Nqa Mémoires

Je vous fournit dans les photos les PCB de txhawb nqa mémoire sur lequel vous pourrez vous inspirer pour vos réalisations. Si vous voulez réaliser un système de mémoire sib pauv tau comme moi veillez bien à câbler kho kom raug vos mémoires en utilisant toujours le même ordre pour les pins.

Si vous avez des cov lus nug remarques n'hésitez pas tout avis est le bienvenu, en espérant vous avoir aidé!

Pom zoo:

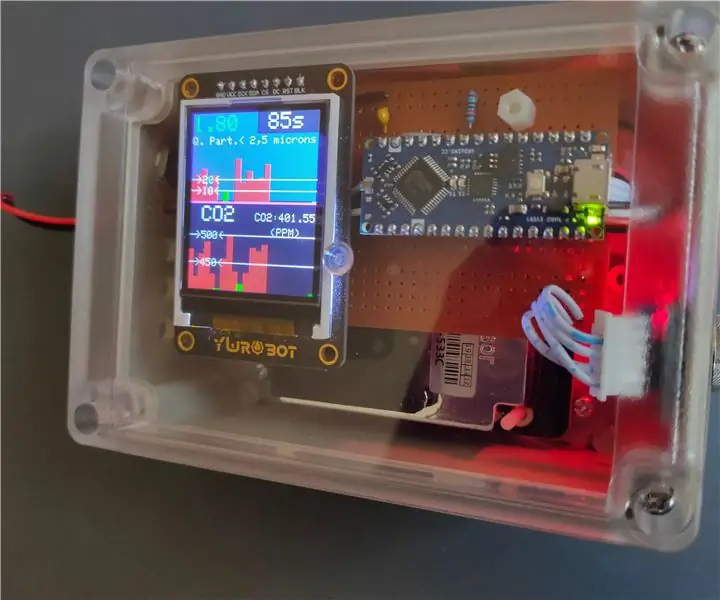

Portable Fine Particle Measurement (Extension): 3 Kauj Ruam

Kev ntsuas qhov ntsuas me me (txuas ntxiv): Lub Hom Phiaj: Ntxiv ntawm CO2 sensor Txhim kho kev nyeem tau zoo ntawm txoj haujlwm Qhib qhov haujlwm mus rau lwm hom kev ntsuas. Txoj haujlwm no ua raws lwm qhov uas twb tau tshaj tawm lawm. Nws teb cov lus nug nug los ntawm cov nyeem. Ib qho ntxiv sensor tau

Chrome Web Extension - Tsis Muaj Kev Paub Ua Ntej Yuav Xav Tau: 6 Cov Kauj Ruam

Chrome Web Extension - Tsis Muaj Kev Paub Coding Ua Ntej Xav Tau: Chrome Extensions yog cov haujlwm me me uas tsim los txhim kho cov neeg siv saib xyuas kev paub. Yog xav paub ntxiv ntawm chrome txuas ntxiv mus rau https://developer.chrome.com/extensions.To ua Chrome Web Extension, yuav tsum muaj coding, yog li nws muaj txiaj ntsig zoo los tshuaj xyuas HT

RaspberryPi 3/4 Extension Board rau Ntxiv Cov Nta Ntxiv rau Raspberry Pi: 15 Cov Kauj Ruam (nrog Duab)

RaspberryPi 3/4 Extension Board rau Ntxiv Nta Ntxiv rau Raspberry Pi: peb paub tias raspberry pi 3/4 tsis tuaj nrog ua hauv ADC (analog to digital converter) thiab RTC (lub sijhawm tiag tiag) yog li kuv tsim PCB uas muaj 16 channel 12bit ADC, RTC, SIM7600 4G module, thawb cov nyees khawm, tso tawm, USB fais fab tawm, 5V fais fab tuag, 12V

Cat Whisker Sensory Extension Wearable (2.0): 6 Cov Kauj Ruam (nrog Duab)

Cat Whisker Sensory Extension Wearable (2.0): Txoj haujlwm no yog txuas ntxiv thiab rov xav txog kuv tus qub phooj ywg (metaterra) " Whisker Sensory Extension Wearable " Lub hom phiaj ntawm txoj haujlwm no yog tsom mus rau kev tsim cov ntawv tshiab, suav nrog kev suav nrog "kev xav txuas ntxiv" uas

Beaglebone Black Web Tswj Siv WebPy: 6 Cov Kauj Ruam

Beaglebone Black Web Control Siv WebPy: Puas xav tsim txoj hauv kev los tswj koj lub qhov rooj qhov rooj siv koj lub xov tooj tej zaum sau cov ntaub ntawv thiab saib nws los ntawm koj lub laptop. Muaj ib lub koos pij tawj lub computer hu ua Beaglebone Black uas yog lub cuab yeej muaj zog uas tso cai rau koj los tswj kuv